Revision 0.1 March 02, 2021

Which Which

**Revision History**

| 3 | - in     | 1/0/2          | Copp. Copp. |                 | Vija - | Vin Vin | Vila . | Chi | N/3 |

|---|----------|----------------|-------------|-----------------|--------|---------|--------|-----|-----|

|   | Revision | Date           | Author      | Description     |        |         |        |     |     |

|   | 0.1      | March 02, 2021 | AWAXXXX     | Initial version |        |         |        |     |     |

# **Contents**

|                  |       | MI      | M,            | MI                                | M.       | M,                  | W.                  | MI     | M. | M. |

|------------------|-------|---------|---------------|-----------------------------------|----------|---------------------|---------------------|--------|----|----|

| Rev              | ision | History | <i>/</i>      |                                   |          |                     |                     |        |    | i  |

| Con              | tents | S       |               |                                   |          |                     |                     |        |    | ii |

| 1                | Abo   | ut This | Document      |                                   |          |                     |                     |        |    | 1  |

|                  | 1.1   | Purpo   | se and Scope  |                                   |          |                     |                     |        |    | 1  |

|                  | 1.2   | Intend  | ded Audience  |                                   |          |                     |                     |        |    | 1  |

|                  | 1.3   | Symbo   | ol Convention | S                                 |          |                     |                     |        |    | 1  |

|                  |       | 1.3.1   | Symbol Con    | ventions                          |          |                     |                     |        |    | 1  |

|                  |       | 1.3.2   | Table Conte   | nt Conventio                      | ons      |                     |                     |        |    | 1  |

|                  |       | 1.3.3   | Reset Value   | Conventions                       | i        |                     |                     |        |    | 1  |

| 1CSL             |       | 1.3.4   | Register Att  | ributes                           | nly Cat  |                     |                     |        |    | 2  |

| 70               |       | 1.3.5   | Numerical S   | ystem                             | Mes      | Mes                 | M.,                 | M, s   | m, | 2  |

| Con              |       |         |               |                                   |          |                     |                     |        |    |    |

| 2                | Prod  | duct De | escription    |                                   |          |                     |                     |        |    | 4  |

|                  |       |         | iew           |                                   |          |                     |                     |        |    |    |

|                  | 2.2   | Featu   | res           |                                   |          |                     |                     |        |    | 4  |

|                  |       | 2.2.1   | CPU Archite   | cture                             | <u> </u> |                     |                     |        |    | 4  |

|                  |       | 2.2.2   | DSP Archite   | cture                             |          |                     |                     |        |    | 4  |

|                  |       | 2.2.3   | Memory Sul    | oSystem                           |          |                     |                     |        |    | 4  |

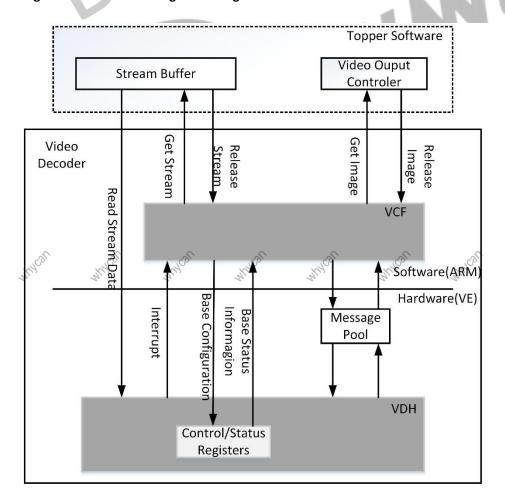

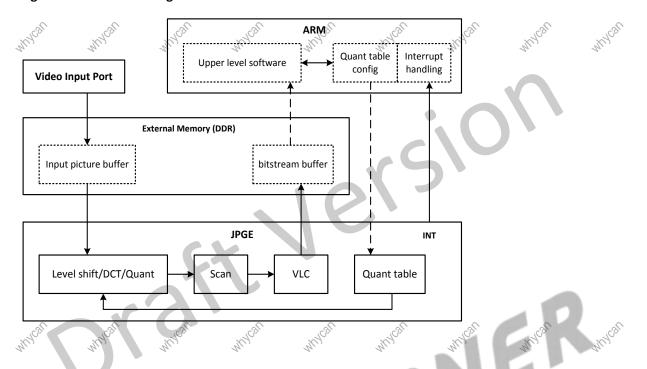

|                  |       | 2.2.4   | Video Engin   | e                                 | /        |                     |                     |        |    | 6  |

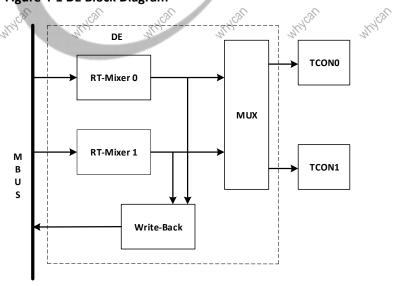

| 2                |       | 2.2.5   |               | raphics                           |          | .0                  |                     |        |    |    |

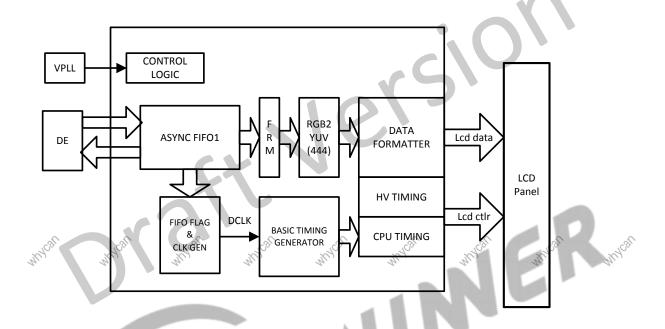

| H <sub>CSI</sub> |       | 2.2.6   | Video Outpu   | ıt <sub>i</sub> nl <sup>çəi</sup> | "ILACOT  | "ILA <sub>COL</sub> | "ILA <sub>SSI</sub> | My Sai |    | 8  |

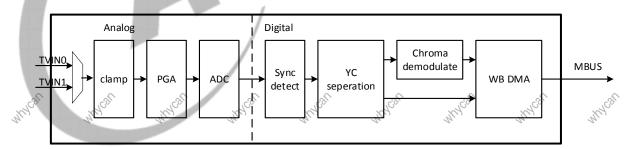

|                  |       | 2.2.7   | Video Input   |                                   |          |                     |                     |        |    | 9  |

|                  |       | 2.2.8   | System Peri   | pherals                           |          |                     |                     |        |    | 10 |

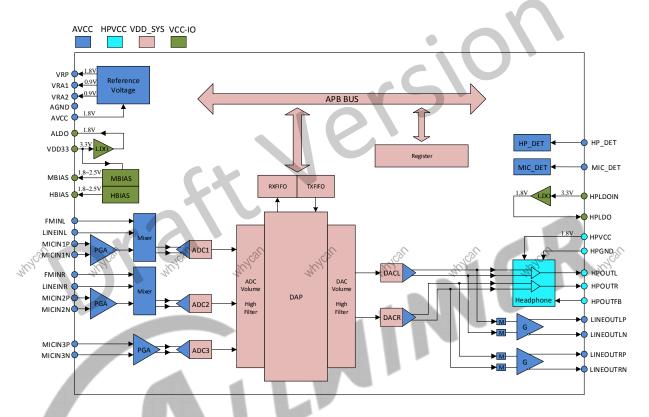

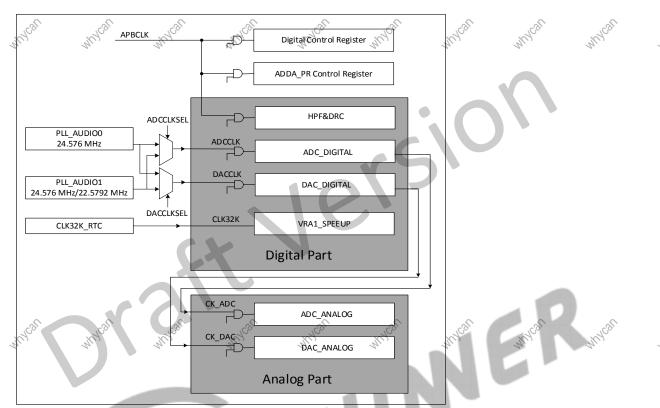

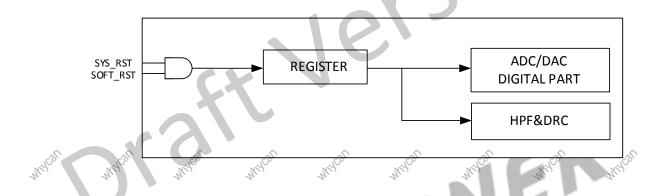

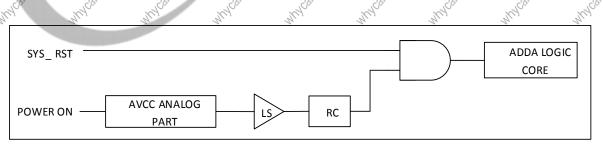

|                  |       | 2.2.9   | Audio Interf  | aces                              |          |                     |                     |        |    | 13 |

|                  |       | 2.2.10  | Security Sys  | tem                               |          |                     |                     |        |    | 15 |

|                  |       | 2.2.11  | External Per  | ipherals                          |          |                     |                     |        |    | 16 |

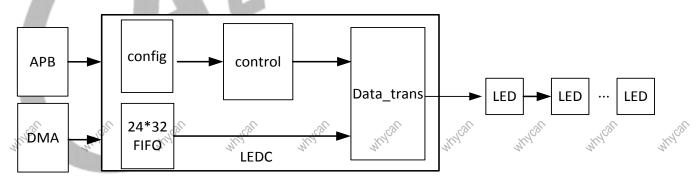

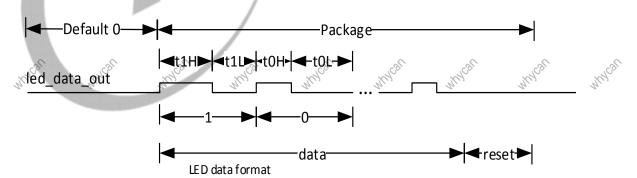

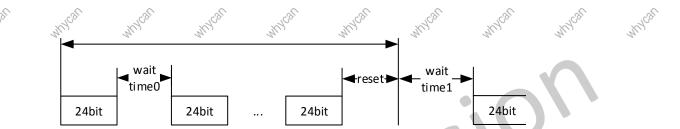

|                  |       | 2.2.12  | 2 LEDC        |                                   |          |                     |                     |        |    | 22 |

|                  |       | 2.2.13  | B Package     |                                   |          |                     |                     |        |    | 23 |

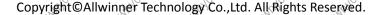

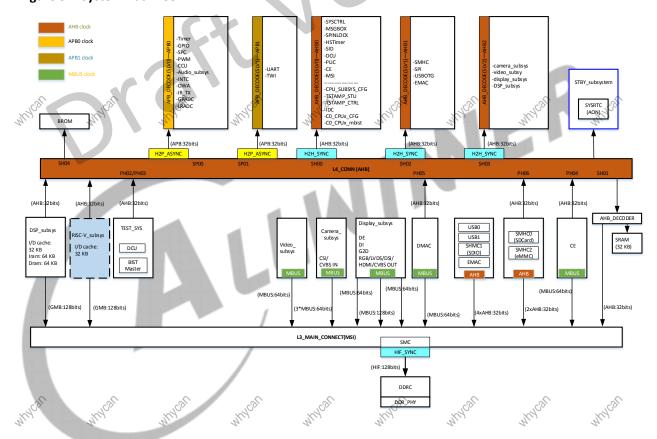

|                  | 2.3   | Block   | Diagram       |                                   |          |                     |                     |        |    | 23 |

| Con              | tents | S       |               |                                   |          |                     |                     |        |    | 25 |

| systo | em     | ntyle ntyles           | whycon   | WHYEST. | whycor. | Mycan  | MyCaff. | nky <sup>CS</sup> |

|-------|--------|------------------------|----------|---------|---------|--------|---------|-------------------|

|       |        | ory Mapping            |          |         |         |        |         |                   |

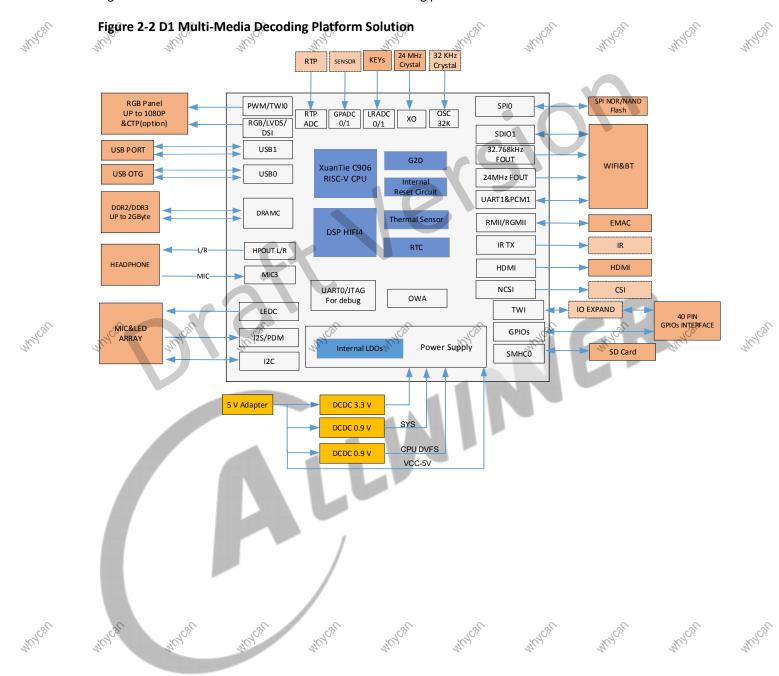

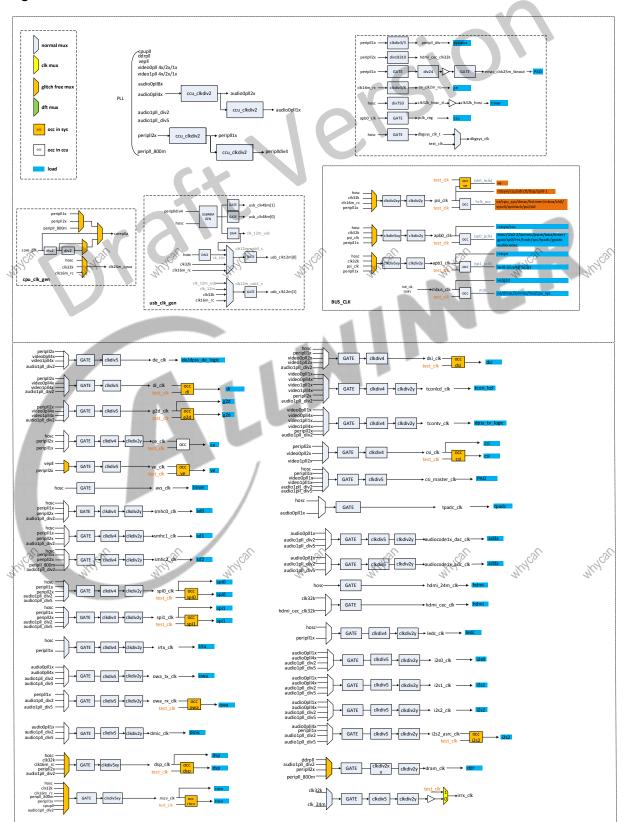

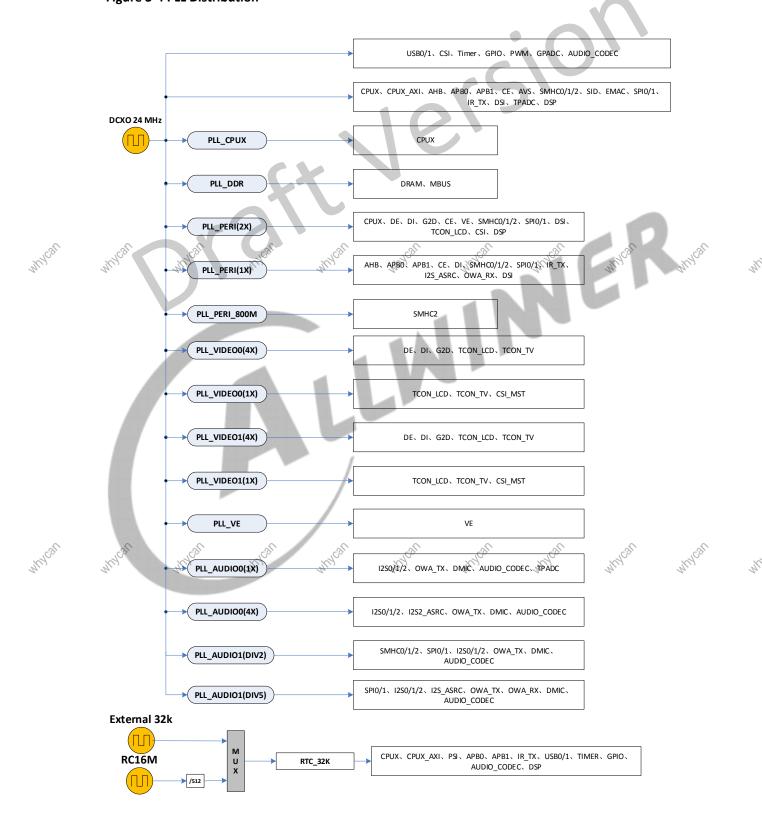

| 3.2   | Clock  | Controller Unit (CCU)  |          |         |         |        |         |                   |

|       | 3.2.1  | Overview               |          |         |         |        |         |                   |

|       | 3.2.2  | Block Diagram          |          |         |         |        |         |                   |

|       | 3.2.3  | Functional Description |          |         |         |        |         |                   |

|       | 3.2.4  | Programming Guidelines | 5        |         |         |        |         |                   |

|       | 3.2.5  | Register List          |          |         |         |        |         |                   |

|       | 3.2.6  | Register Description   |          |         |         |        |         |                   |

| 3.3   | BROM   | 1 System               |          |         |         |        |         |                   |

|       | 3.3.1  | Overview               |          | jr.yesi |         | ik ker | WAGEL   | ye.ye             |

|       | 3.3.2  | Functional Description |          |         |         |        |         |                   |

| 3.4   | Syster | m Configuration        |          |         |         |        |         |                   |

|       | 3.4.1  | Overview               |          |         |         |        |         |                   |

|       | 3.4.2  | Register List          |          |         |         |        |         |                   |

|       | 3.4.3  |                        |          |         |         |        |         |                   |

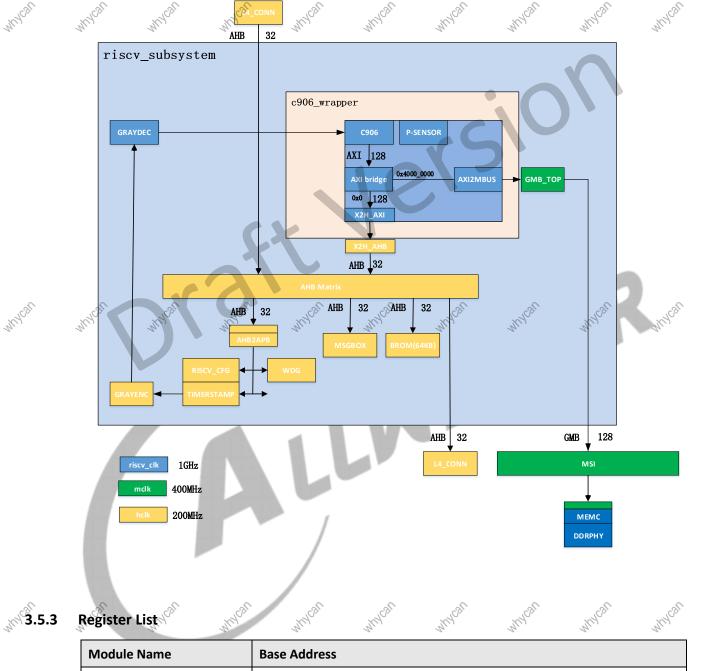

| 3.5   | RISC-V | / System               |          |         |         |        |         |                   |

|       | 3.5.1  | Overview               | <u> </u> |         |         |        |         |                   |

|       | 3.5.2  | Block Diagram          |          |         |         |        |         |                   |

|       | 3.5.3  | Register List          |          |         |         |        |         |                   |

|       | 3.5.4  | Register Description   |          | 26,     | 2       | 263,   | 2       |                   |

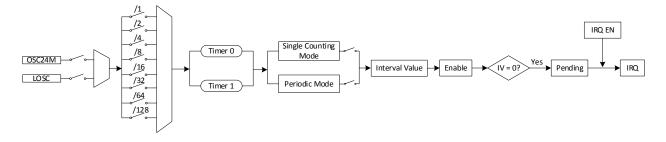

| 3.6   | Timer  | Register Description   | MA       | Meg     | MA      | WEST   | Med     | ikili             |

|       | 3.6.1  | Overview               |          |         |         |        |         |                   |

|       | 3.6.2  | Block Diagram          |          |         |         |        |         |                   |

|       | 3.6.3  | Functional Description |          |         |         |        |         |                   |

|       | 3.6.4  | Programming Guidelines | 5        |         |         |        |         |                   |

|       | 3.6.5  | Register List          |          |         |         |        |         |                   |

|       | 3.6.6  | Register Description   |          |         |         |        |         |                   |

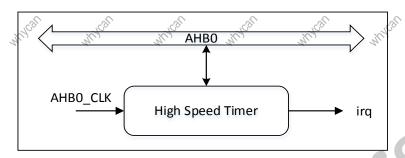

| 3.7   | High S | Speed Timer            |          |         |         |        |         |                   |

|       | 3.7.1  | Overview               |          |         |         |        |         |                   |

|       | 3.7.2  | Block Diagram          |          |         |         |        |         |                   |

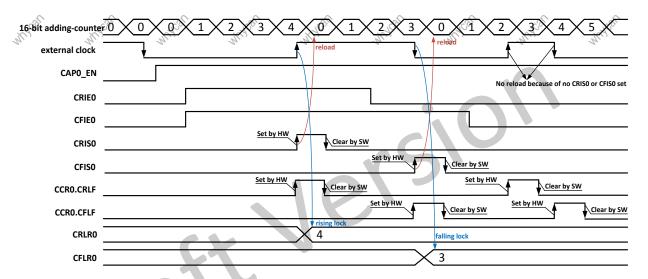

|      | 3.7.3   | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 190 |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 3.7.4   | Programming Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 193 |

|      | 3.7.5   | Programming Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 194 |

|      | 3.7.6   | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 3.8  | Platfor | rm-Level Interrupt Controller (PLIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 202 |

|      | 3.8.1   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | 3.8.2   | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | 3.8.3   | Register List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | 3.8.4   | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 209 |

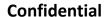

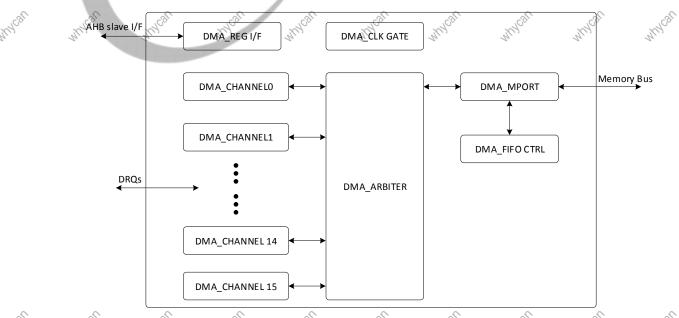

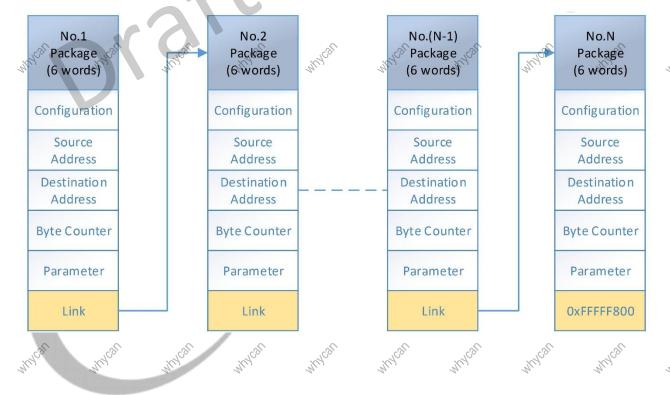

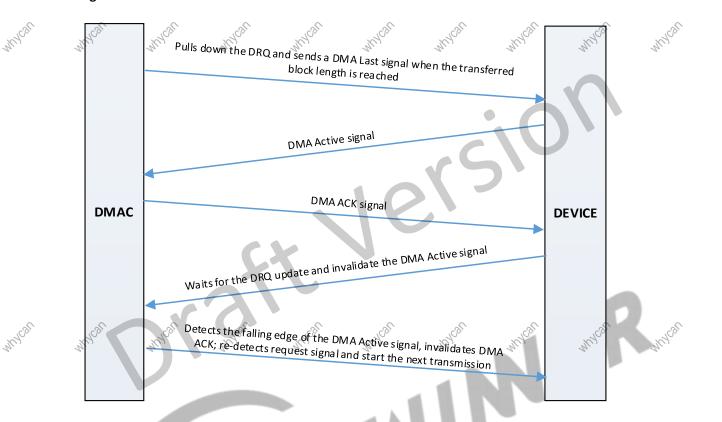

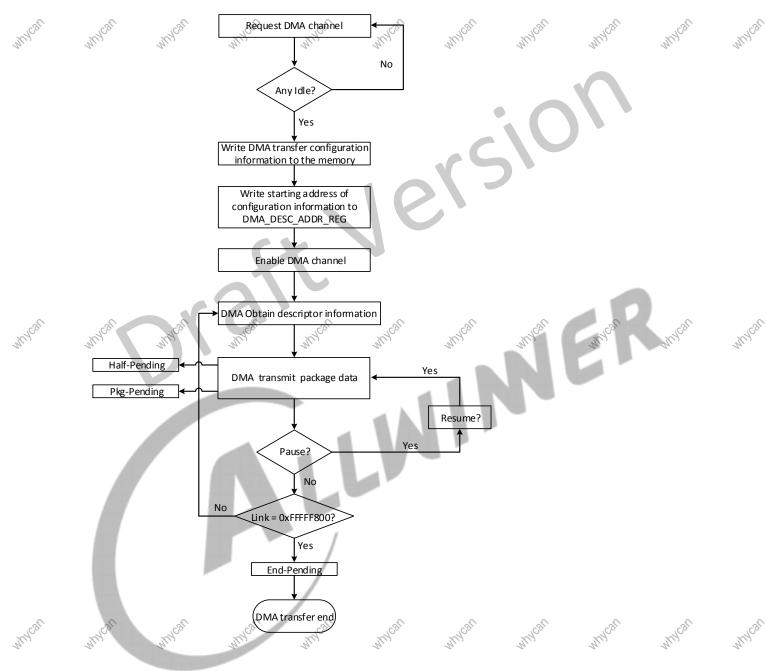

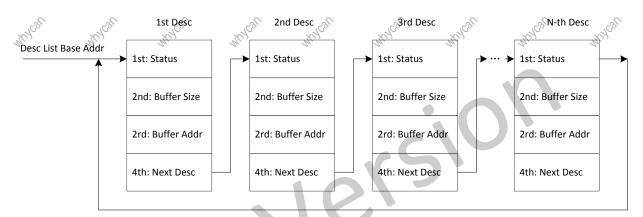

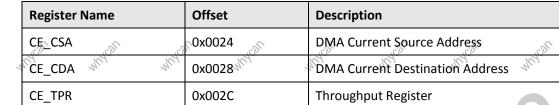

| 3.9  | Direct  | Memory Access Controller (DMAC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 213 |

|      | 3.9.1   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | 3.9.2   | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | 3.9.3   | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 214 |

|      | 3.9.4   | Programming Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|      | 3.9.5   | Register List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | 3.9.6   | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 227 |

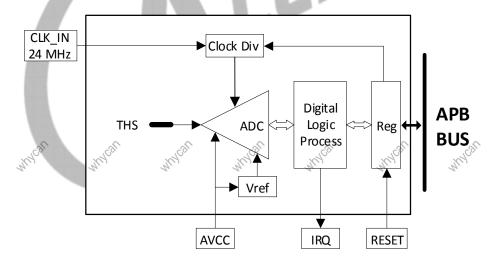

| 3.10 |         | al Sensor Controller (THS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

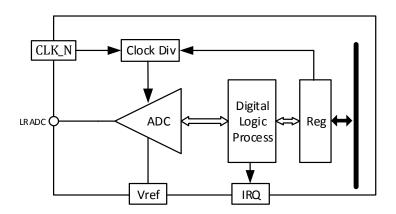

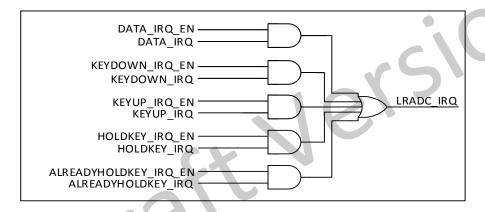

|      |         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | 3.10.2  | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 247 |

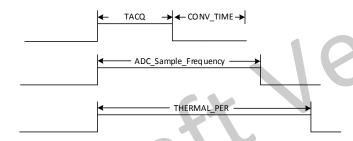

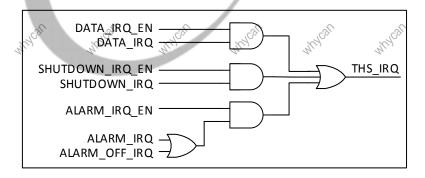

|      | 3.10.3  | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 247 |

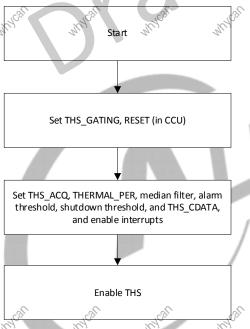

|      | 3.10.4  | Programming Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 249 |

|      |         | Register List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | 3.10.6  | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 251 |

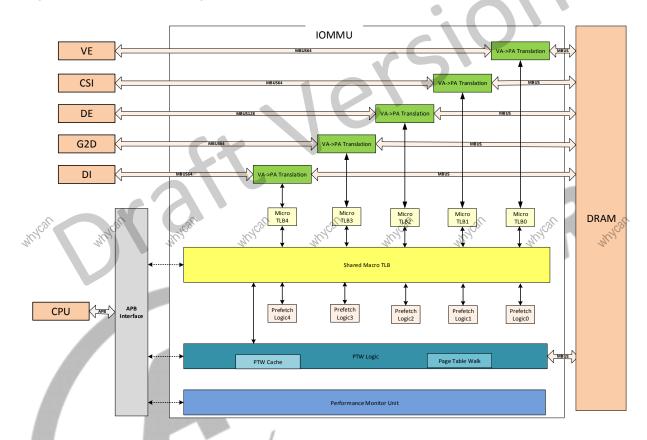

| 3.11 | ОММ     | Register Description of the second of the se | 257 |

|      | 3.11.1  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 257 |

|      | 3.11.2  | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 257 |

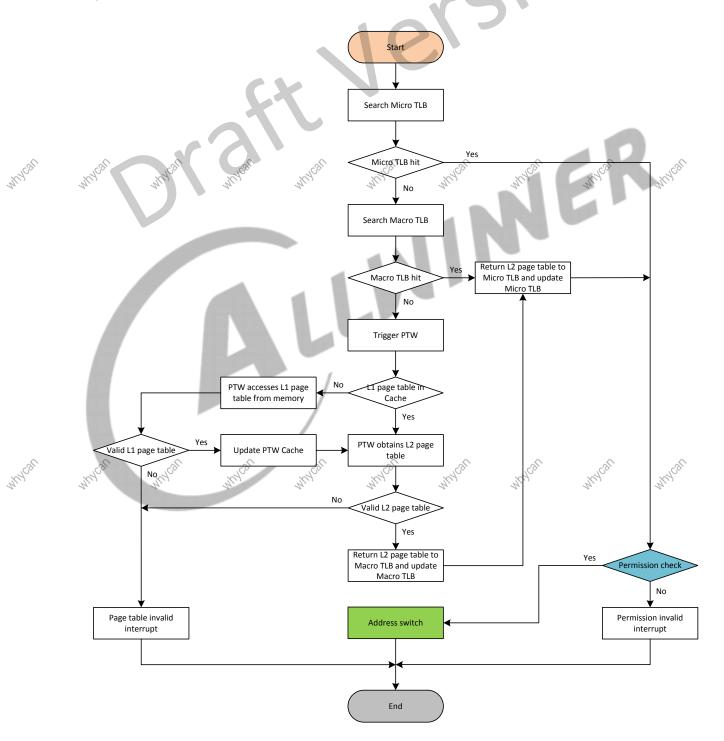

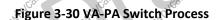

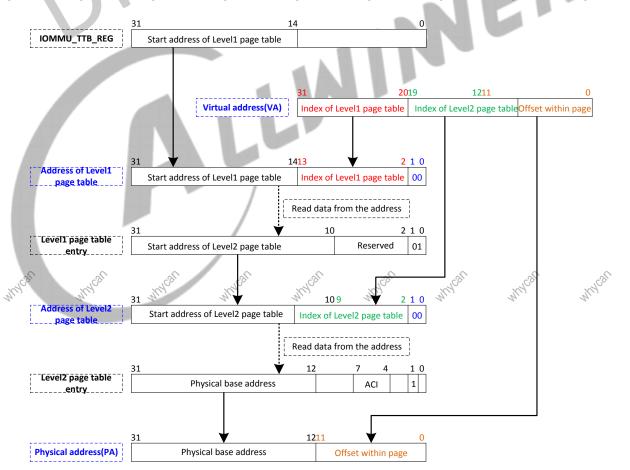

|      | 3.11.3  | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 258 |

|      | 3.11.4  | Programming Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 268 |

|      | 3.11.5  | Register List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 270 |

|      | 3.11.6  | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 273 |

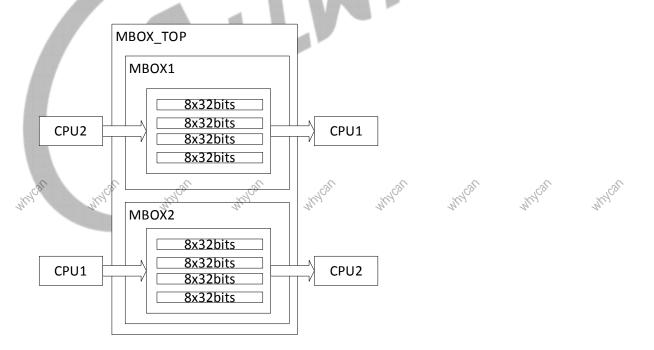

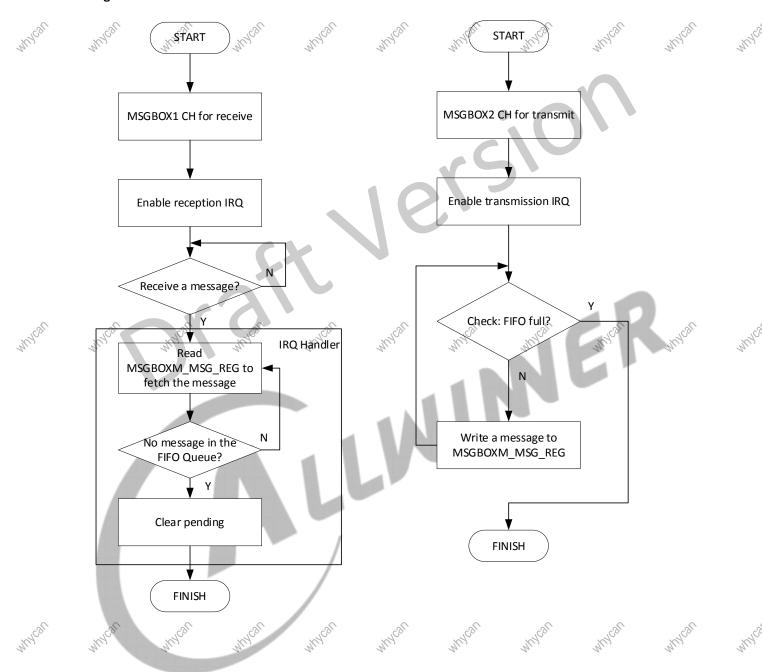

| 3.12 | . Messa | ge Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 343 |

|      | 3.12.1  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 343 |

|      | 3.12.2  | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 343 |

|        |        | 3.12.3 | Functional Des               | cription   |     |                 |                   |                   |                   | 344                 |

|--------|--------|--------|------------------------------|------------|-----|-----------------|-------------------|-------------------|-------------------|---------------------|

| 183.   |        | 3.12.4 | Programming (                | Guidelines |     |                 |                   |                   |                   | 345                 |

| 11/2   |        | 3.12.5 | Programming of Register List | MA         | MM  | <sup>N</sup> CM | Mr.               | M <sup>2</sup>    | Meg.              | <sup>yhyo</sup> 346 |

|        |        | 3.12.6 | Register Descr               | iption     |     |                 |                   |                   |                   | 347                 |

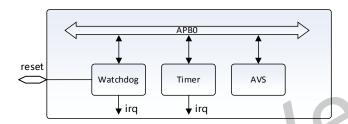

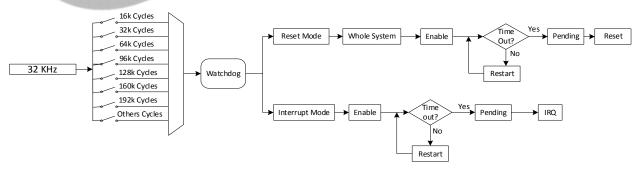

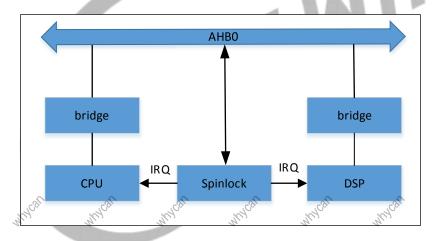

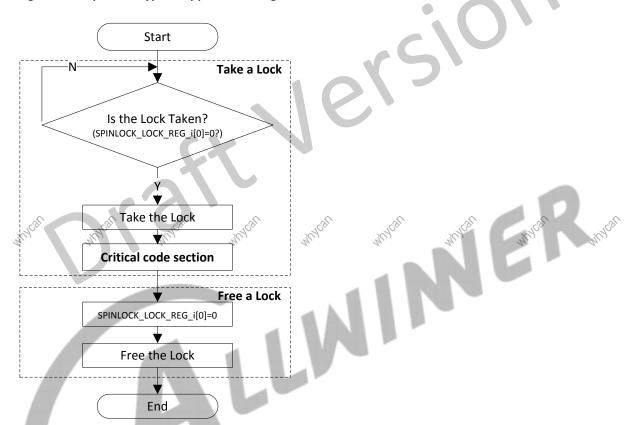

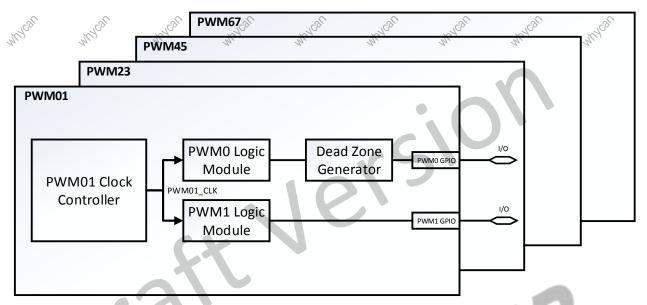

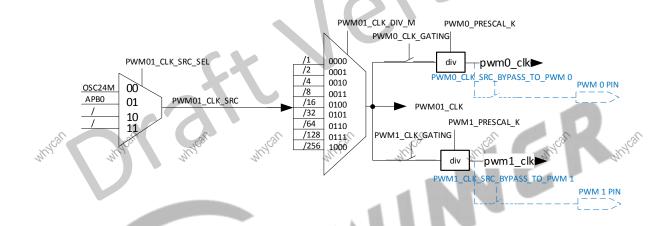

|        | 3.13   | •      | ock                          |            |     |                 | 1                 |                   |                   |                     |

|        |        |        | Overview                     |            |     |                 |                   |                   |                   |                     |

|        |        |        | 2 Block Diagram              |            |     |                 |                   |                   |                   |                     |